Project Details

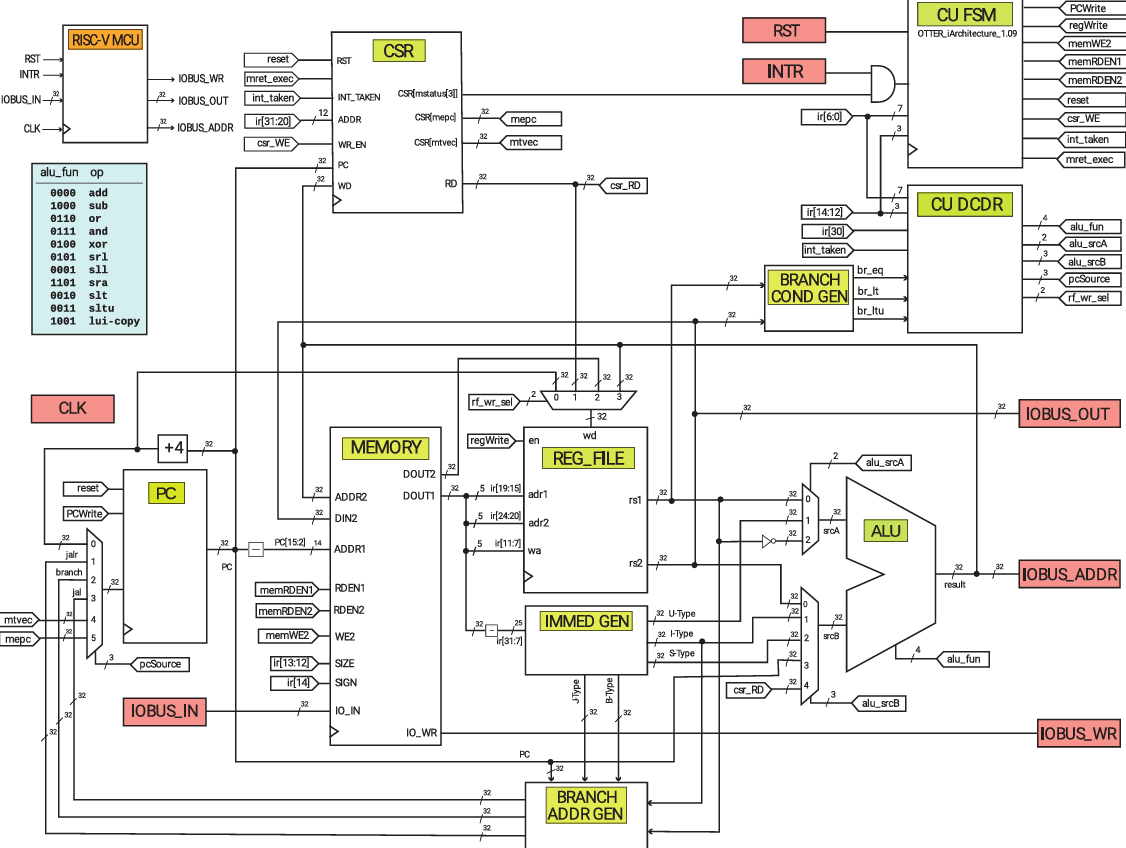

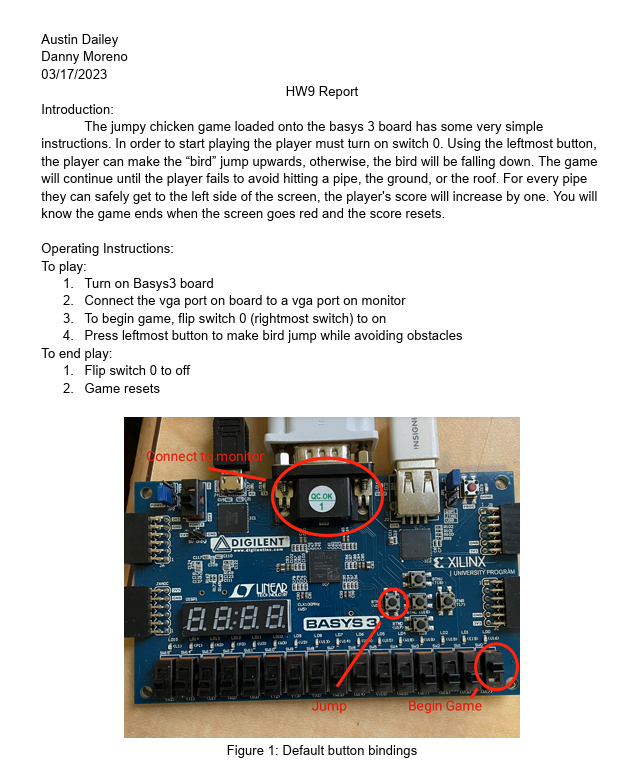

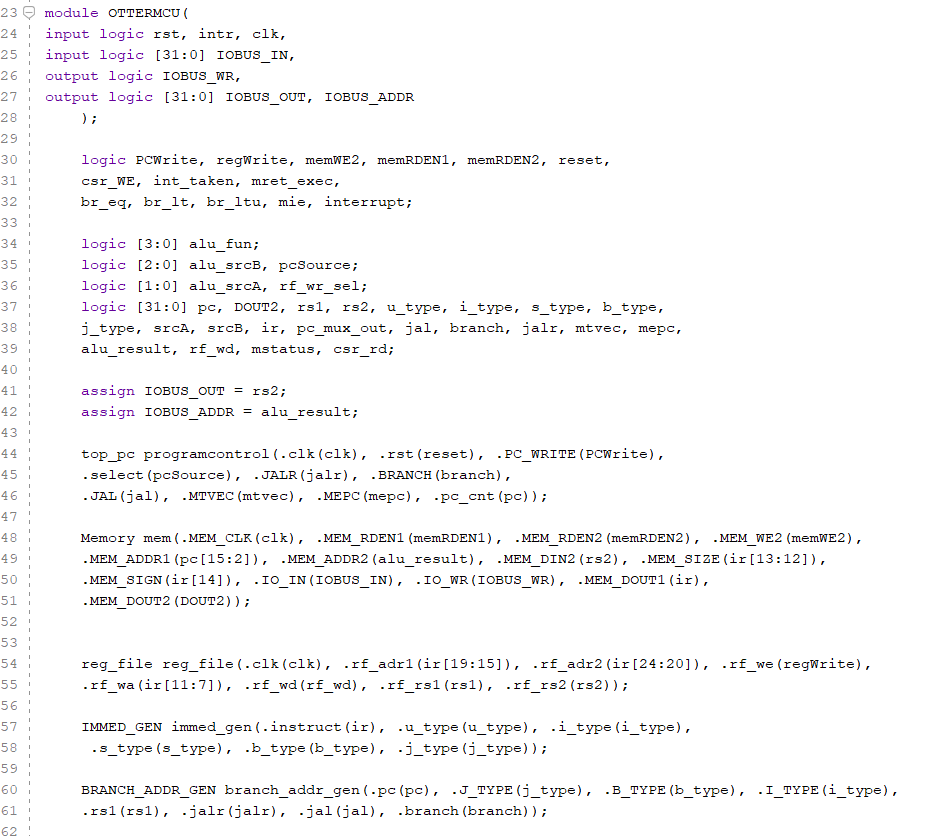

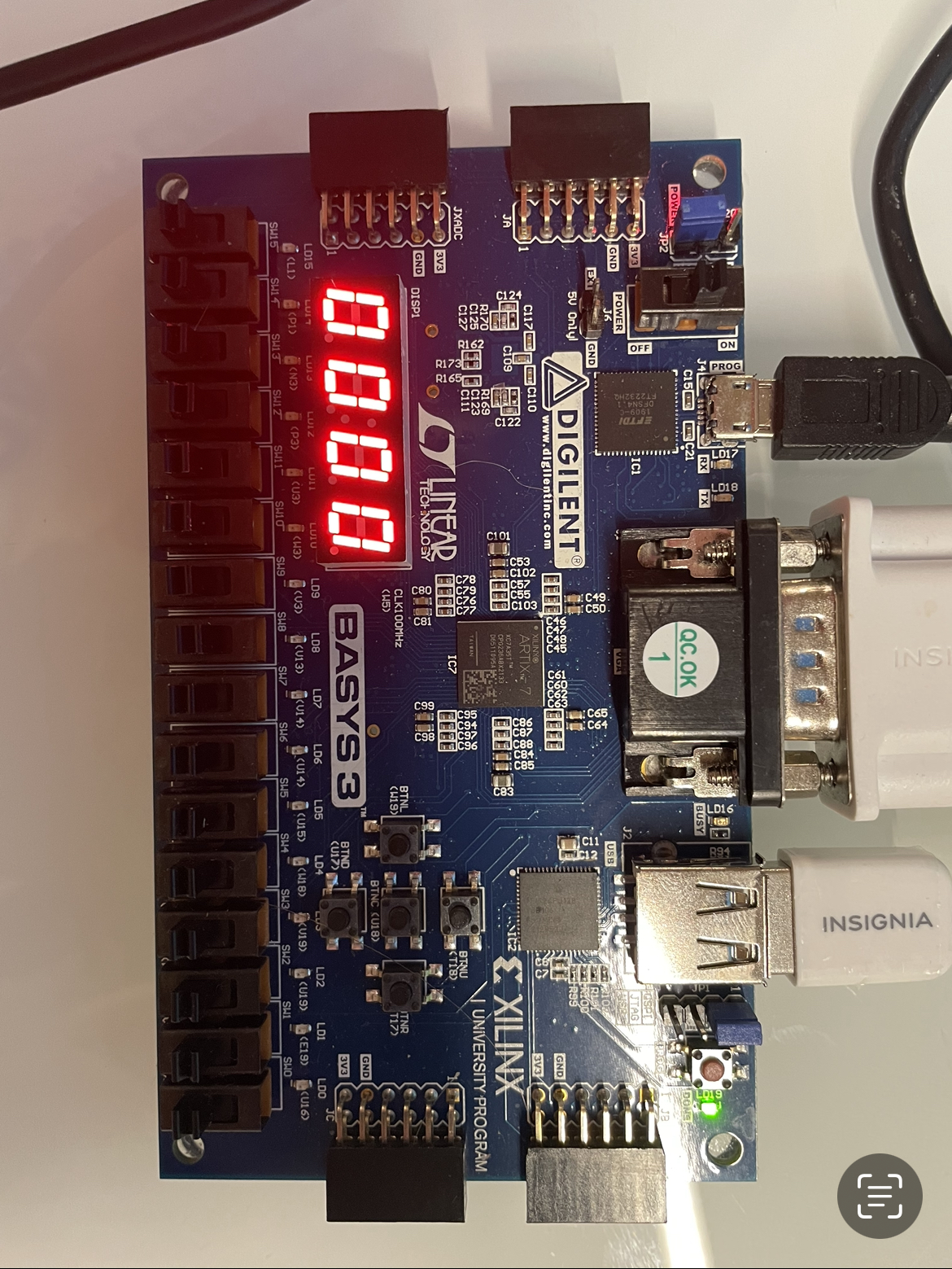

This was a quarter-long project that began with the development of each module of the RISC-V MCU(see below for module map). After every module was written in Vivado(verilog), it was tested to ensure its functionality seperate from other modules. This made the process of debugging in the final project much easier as I did not have to search through hours of hardware code to ensure the error was in my assembly code. Once the MCU was completed and all modules were linked together, we were able to then write assembly code which would effectively run on the MCU with full function, inlcuding interrupts. Some specifc skills that this project improved were:

- Verilog language

- Assembly language

- Hardware Debugging

- Project management and design

- Interfacing with new IO